**NUSOD 2021**

# Modeling of polarization-rotation based photonic D flip-flop using a compact micro-ring resonator

Gaurav Kumar Bharti Electronics and Electrical Engineering Department Indian Institute of Technology Guwahati Guwahati, Assam, India gkbharti@iitg.ac.in

Abstract— This paper demonstrates the modeling and simulation of all-optical polarization rotation based clocked D flip-flop using a single micro-ring resonator. The simulated results show the switching time of 0.5 ps and the on-off ratio of 25.27 dB.

Keywords- all-optical switch, FDTD simulation, micro-ring resonator, optical flip-flop, polarization rotation

### I. INTRODUCTION

The flip-flops (FFs) are sequential logic circuits used for memory storage in digital form. The D-FF is a Delay FF having one-bit arithmetical memory. D-FF can be designed using the concept of electro-optic effect in the micro-ring resonator (MRR) [1] and Mach-Zehnder Interferometer [2]. In the present paper the implementation of D-FF is all-optical in nature with simple architecture [3-5], where polarization states are manipulated and the specific logic relationship has been obtained between the input and output signal. The output state of the polarized light is dependent on the nature of the polarization rather than its intensity.

## II. THEORY AND OPERATION OF THE PROPOSED MODEL

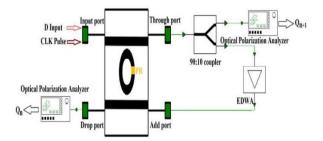

The schematic of the proposed structure comprises of an MRR, a polarization-rotator (PR), and a fedback loop called an erbium-doped waveguide amplifier (EDWA) [6-7] is shown in Fig. 1. The PR is used to rotate the axis of unpolarized light to the polarized light by an angle of choice due to its birefringence effect. To realize the all-optical flip-flop switching, the EDWA is employed in the proposed design which is used to amplify the fedback signal and to provide the delay in the circuit [5]. The parameters used for modeling the device are given in Table I.

Fig. 1. Schematic diagram of the proposed model

Ramesh Kumar Sonkar Electronics and Electrical Engineering Department Indian Institute of Technology Guwahati Guwahati, Assam, India sonkar@iitg.ac.in

TABLE I PARAMETERS USED FOR MODELLING

| Parameters                  | Description         |  |

|-----------------------------|---------------------|--|

| Material combination        | Si-SiO <sub>2</sub> |  |

| Gain of EDWA                | 3 dB                |  |

| Insertion loss              | 0.0002 dB           |  |

| Circumference of the MRR    | 62.8 µm             |  |

| Coupling coefficient of MRR | TE = 0.2, TM = 0.15 |  |

| Height of the waveguide     | 0.2 μm              |  |

| Width of the waveguide      | 0.4 μm              |  |

# RESULT AND DISCUSSIONS

In the D-FF, if the clock pulse is at "logic 1" or high, the output of D-FF ( $Q_{n+1}$ ) is as same as D input and if the clock signal is at "logic 0" or low, the FF holds the data of the previous state. The input of the D-FF is active only when the control pulse is high. Thus, the D-FF is a controlled bi-stable latch.

III.

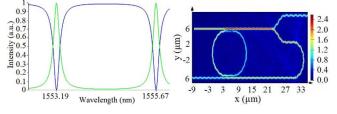

For realizing the D-FF in the proposed device, "logic 1" or high is considered as horizontal polarized light (HPL), and "logic 0" or low is considered as vertical polarized light (VPL) respectively. The proposed MRR changes its output polarized state if the suitable nature of the pump pulse is injected. The corresponding transmission of the MRR and the electric field evolution in the proposed device are shown in Fig. 2 (a) and 2 (b) respectively.

Fig. 2. (a). Output transmission of the MRR (b). Electric field evolution of the proposed model

To realize the FF, the D-input as well as the clock signal (CLK) are injected from the input port at resonance wavelengths ( $\lambda_r$ ) of 1555.67 nm and 1553.19 nm respectively, through the coupler. At  $\lambda_r =$  1555.67 nm, the polarization-rotation is realized at the outputs of the device through the optical polarization analyzer in terms of azimuth angle. The VPL has azimuth angle near to 90° and HPL has azimuth angle near to 0°. The output obtained from the through port via a Y-coupler (90:10 coupler) called the Q<sub>n+1</sub>, and the rest part of the light is

amplified by the EDWA and fedback to MRR through the add port. The strong CLK pulse allows the output  $(Q_{n+1})$  to alter its state; otherwise, it holds the former state. The PR has been fixed to provide a rotation of 30°. The various logical combinations for the proposed D-FF are as follows;

Case-1: D = CLK = HPL ("logic 1"),  $Q_n = HPL$  ("logic 1")

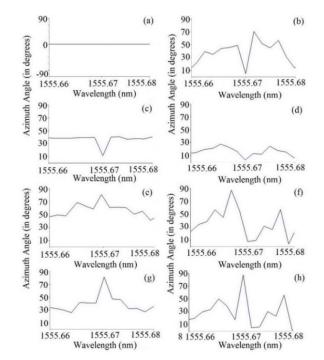

If the previous state ( $Q_n$ ) is HPL, an optical pulse will reach at the add port passing through the fedback path. The signals are present at the input port and add port. When CLK is applied simultaneously, therefore, according to the principle of MRR, the D input is propagated towards the through port [5]. Consequently, the FF's next state ( $Q_{n+1}$ ) is HPL. The graph in Fig. 3 (a) and Fig. 3 (b) shows the azimuth angle of 0° and less than 10° indicates the HPL at the output. Case-2:  $D = Q_n = HPL$  ("logic 1"), CLK= VPL ("logic 0")

Similar to the previous case, the output signal arrives at add port after passing through the loop with the same instant of input D. Due to the low CLK pulse, the output nature of HPL is obtained at the through port, as shown in Fig. 3 (c). As the CLK signal is low (or VPL), therefore, according to the principle of MRR, the input optical signal is directed towards the drop port [5]. At the same instant, the signal of add port will be directed towards the through port of the MRR. The output is same as the previous state as shown in Fig. 3 (d).

Case-3: D = VPL ("logic 0"),  $CLK = Q_n = HPL$  ("logic 1")

When a strong CLK of HPL is injected into the device, the input D has been directed towards the through port. As a result,  $Q_{n+1}$  of VPL is observed at the output. The output of  $Q_{n+1}$  and  $Q_n$  is shown in Fig. 3 (e) and Fig. 3 (f) which indicates the azimuth angle of 80° and 10° and confirms the VPL and HPL respectively.

Case-4:  $D = Q_n = CLK = VPL$  ("logic 0")

When the D-input is VPL as well as low CLK is applied to the device, the output of D-FF would be low, as shown in Fig. 3 (g) and Fig. 3 (h). The simulated results are summarized in Table II.

The performance of the device depends on the gain of the amplifier, the rotation angle of the PR, and the geometrical parameters of the device. The all-optical switching behaviour of the MRR is dependent on the circumference, which also determines resonance condition and thus, free-spectral range (FSR). The comparison of the proposed work with the recent literatures is shown in Table III.

TABLE II TRUTH-TABLE OF THE PROPOSED D-FF

| D input          | CLK              | Q n+1            | Qn            | Remarks   |

|------------------|------------------|------------------|---------------|-----------|

| "logic 1"<br>HPL | "logic 1"<br>HPL | "logic 1"<br>HPL | "logic 1" HPL | Set       |

| "logic 1"        | "logic 0"        | "logic 1"        | "logic 1" HPL | Unchanged |

| HPL<br>"logic 0" | VPL<br>"logic 1" | HPL<br>"logic 0" | "logic 1" HPL | Reset     |

| <b>V</b> PL      | HPL              | <b>V</b> PL      | 2             |           |

| "logic 0"<br>VPL | "logic 0"<br>VPL | "logic 0"<br>VPL | "logic 0" VPL | Unchanged |

TABLE III COMPARISON WITH THE LITERATURES

| References | Parameters    |        |              |                 |  |  |

|------------|---------------|--------|--------------|-----------------|--|--|

|            | Circumference | FSR    | On-off ratio | Response time   |  |  |

| [1]        | 60 µm         | -      | -            | 0.04 ns         |  |  |

| [5]        | 44.5 μm       | -      | 21 dB        | 1.6 ps          |  |  |

| This work  | 62.8 µm       | 2.5 nm | 25.27 dB     | 0.5 ps ; 0.6 ps |  |  |

Fig. 3. (a)-(h). Outputs of the proposed model in terms of azimuth angle

IV.

### CONCLUSIONS

This paper demonstrates the polarization rotation based MRR for D-FF switching. The simulation results verified its successful operation. The model shows the on-off ratio of 25.27 dB and the response time of 0.5 ps. The FSR has been obtained as high as 2.5 nm. The model may be used for obtaining other sequential, combinational circuits and is suited for interconnects within micro or sub-microchips.

#### ACKNOWLEDGMENT

This research is supported by the Ministry of Electronics and Information Technology, Science and Engineering Research Board, and the Department of Science & Technology, Government of India.

#### References

- F. K. Law, M. R. Uddin, and H. Hashim, "Photonic D-type flip flop based on micro-ring resonator," *Optical and Quantum Electronics*, vol. 50, 2018.

- [2] S. Kumar, G. Singh, A. Bisht, and A. Amphawan, "Design of D flip-flop and T flip-flop using Mach-Zehnder interferometers for high-speed communication," *Applied Optics*, vol. 54, pp. 6397-6405, 2015.

- [3] C. Reis et al, "Performance comparison of all-optical clocked S-R and D type flip-flops," *Optik-International Journal for Light and Electron Optics*, vol. 124, pp. 2327-2333, 2013.

- [4] G. K. Bharti, and J. K. Rakshit, "Design of all-optical JK, SR and T flip-flops using micro-ring resonator-based optical switch," *Photonic Network Communications*, vol. 35, pp. 381-391, 2018.

- [5] J. K. Rakshit, J. N. Roy, and T. Chattopadhyay, "A theoretical study of all optical clocked D flip flop using single micro-ring resonator," *Journal of Computational Electronics*, vol. 13, pp. 278-286, 2014.

- [6] J. Li, L. Li, L. Jin, and C. Li, "All-optical switch and limiter based on nonlinear polarization in Mach–Zehnder interferometer coupled with a polarization-maintaining fiber-ring resonator," *Optics Communications*, vol. 260, pp. 318-323, 2006.

- [7] J. K. Rakshit, K. E. Zoiros, and G. K. Bharti, "Proposal for ultrafast alloptical pseudo random binary sequence generator using microring resonator-based switches," *Journal of Computational Electronics*, vol. 20, pp. 353-367, 2020.