# **NUSOD 2021**

# Simulation and design of plasmonic directional couplers: application to interference-based all-optical gates

Mohammadamin Ghomashi<sup>\*</sup>, Alberto Tibaldi<sup>\*†</sup>, Francesco Bertazzi<sup>\*†</sup>, Marco Vallone<sup>\*</sup>, Michele Goano<sup>\*†</sup>, and Giovanni Ghione<sup>\*</sup>

\* Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy

<sup>†</sup> CNR-IEIIT c/o Politecnico di Torino, 10129 Turin, Italy

E-mail: mohammadamin.ghomashi@polito.it

Abstract—The paper is focused on the design of optical components based on plasmonic multi-slot directional couplers. In particular, the design of an all-optical gate is proposed, whose operation is based on the coupling between three plasmonic slots. The device input wavelength is 1550 nm, typical of long-haul telecommunication systems. The device footprint is as small as  $11 \times 6 \,\mu\text{m}^2$  and the contrast ratio as an AND gate is about 5.8 dB. The two well-known Finite-Difference Time-Domain (FDTD) and Finite-Difference Eigenmode (FDE) methods are used for the device simulation and optimization.

#### I. INTRODUCTION

All-optical gates and switches have been proposed both as an alternative to electro-optic components for optical routing/switching and as a building block for logical circuits overcoming fundamental limitations of electronic circuits [1]. All-optical gates typically require optical nonlinearities, see e.g. [2], but interference-based designs using linear materials have also been proposed, that are easier to fabricate [3], [4]. All-optical gates may exploit different device concepts, like the Mach-Zehnder interferometer [5], [6], the ring resonator [7] and, for interference-based gates, the Y-junction [3]. In this work, we present an interference-based all-optical gate exploiting plasmonic directional couplers. After preliminary studies on coupled plasmonic slot waveguides, the geometry is discussed and simulated with FDTD and FDE codes [8].

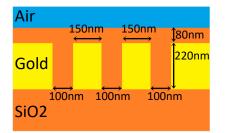

Fig. 1. Geometry of the three-slot directional coupler.

#### II. THE PLASMONIC DIRECTIONAL COUPLER

The plasmonic slot consists of a dielectric layer  $(SiO_2 here)$  sandwiched between two metal layers (Au). If the three

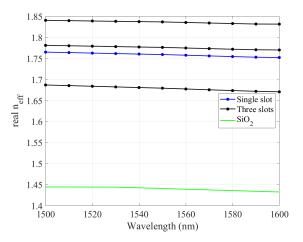

slots are close enough, the optical power is coupled between them. Fig. 1 shows the cross section of a directional coupler consisting of three coupled plasmonic slots. The width of each slot is 100 nm and the distance between slots is 150 nm. Also, the height of slot is designed to be 220 nm. The plasmonic effective refractive index  $n_{\rm eff}$  is computed for a single slot and for the three-slot structure through the FDE method. Fig. 2 compares the modal plasmonic refractive indexes with that of  $SiO_2$ . For a single slot, there is a single propagating mode, with effective refractive index larger than that of  $SiO_2$ . For the three-slots coupler, three propagating modes exist, corresponding to globally odd and even field distributions in the coupled slots. The splitting in the refractive indexes increases with slot coupling and, in general, the geometry can operate as a directional coupler. If the optical power enters one of the directional coupler slots, after propagating for a certain coupling length, power is coupled to the other slots.

Fig. 2. Effective refractive index  $n_{\rm eff}$  of the single plasmonic slot and of the three-slot coupler versus wavelength.

## III. All-optical gate geometry and operation

All-optical interference-based gates (AND, OR, XOR) can be designed exploiting a three-slot directional coupler (instead

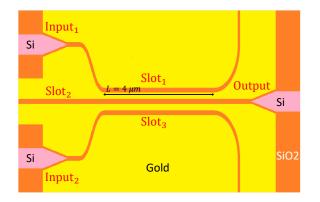

Fig. 3. Layout of the proposed AND plasmonic gate with photonic waveguide inputs and output.

of a Y-junction, as in [2]) as a power combiner. In this paper we concentrate on a gate that, with proper definition of the logical levels, operates as an AND gate. The gate geometry is shown in Fig. 3. The optical power from  $Input_1$  and  $Input_2$ are converted to  $Slot_1$  and  $Slot_3$ , respectively, corresponding to the excitation of coupled modes. At the end of the coupler, the power in  $Slot_2$  is converted into the output silicon photonic waveguide.

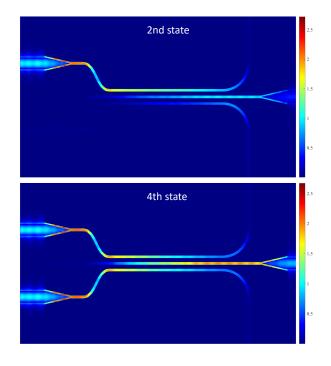

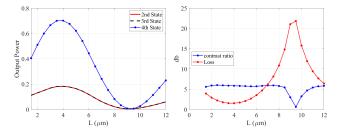

From a logical standpoint, four states can occur: in State 1, both inputs have zero optical power and the output power is zero. In the State 2 (State 3), the optical power only enters Input<sub>1</sub> (Input<sub>2</sub>) and the output/input power ratio is 0.18. In State 4 the two input powers are equal and the output/input power ratio (where the input power is the one in each of the inputs) is 0.70. If output powers below 0.5are considered as a logical 0, the geometry operates as an AND gate according to the truth tabel in Table I. Fig. 4 shows the absolute value of electric field for State 2 and 4; the output power ratio between State 4 and State 2 (State 3) is about 5.8 dB. The aforementioned values were obtained by optimizing the coupler length L that affects the output/input power ratio in all logical states, as shown in Fig. 5; the contrast ratio between State 4 and State 2 (State 3) weakly depends on L, while, for  $L \approx 4 \,\mu \text{m}$  (the selected design value), the optical insertion loss is minimum.

TABLE I Truth table of AND gate

| $\mathbf{Input}_1$ | Input <sub>2</sub> | Output | Power Value |

|--------------------|--------------------|--------|-------------|

| 0                  | 0                  | 0      | 0           |

| 1                  | 0                  | 0      | 0.18        |

| 0                  | 1                  | 0      | 0.18        |

| 1                  | 1                  | 1      | 0.70        |

### **IV. CONCLUSIONS**

In this simulation study, a multi-slot plasmonic directional coupler is proposed with application to the design of an AND all-optical gate gate. The gate size is about  $11 \times 6 \,\mu\text{m}^2$ , making it suitable for integration and also, from a material standpoint, directly compatible with CMOS platforms.

Fig. 4. The electric field for State 2 (above) and State 4 (below).

Fig. 5. Left: output power versus the directional coupler length L. Right: contrast ratio and losses versus L.

#### REFERENCES

- P. Singh, D. K. Tripathi, S. Jaiswal, and H. Dixit, "All-Optical Logic Gates: Designs, Classification, and Comparison." *Adv. in Opt. Tech.*, p. 275083, 2014.

- [2] A. Lattes, H. Haus, F. Leonberger, and E. Ippen, "An ultrafast all-optical gate," *IEEE J. Quantum Electron.*, vol. 19, no. 11, pp. 1718–1723, 1983.

- [3] Y. Fu, X. Hu, C. Lu, S. Yue, H. Yang, and Q. Gong, "All-Optical Logic Gates Based on Nanoscale Plasmonic Slot Waveguides," *Nano Letters*, vol. 12, no. 11, pp. 5784–5790, Nov 2012.

- [4] Z. Li, Z. Chen, and B. Li, "Optical pulse controlled all-optical logic gates in SiGe/Si multimode interference," *Opt. Express*, vol. 13, no. 7, Feb 2005.

- [5] A. Tibaldi, M. Ghomashi, F. Bertazzi, M. Goano, M. Vallone, and G. Ghione, "Plasmonic-organic hybrid electro/optic Mach-Zehnder modulators: from waveguide to multiphysics modal-FDTD modeling," *Opt. Express*, vol. 28, no. 20, pp. 29253–29271, Sep 2020.

- [6] S. Lee, J. Park, K. Lee, D. Eom, S. Lee, and J. H. Kim, "All-Optical Exclusive NOR Logic Gate Using Mach-Zehnder Interferometer," *Jpn. J.* of Appl. Phys., vol. 41, no. Part 2, No. 10B, pp. L1155–L1157, oct 2002.

- [7] A. Salmanpour, S. Mohammadnejad, and P. T. Omran, "All-optical photonic crystal NOT and OR logic gates using nonlinear Kerr effect and ring resonators," *Opt. Quantum Electron.*, vol. 47, no. 12, pp. 3689– 3703, Dec 2015.

- [8] "Lumerical Inc." 2019. [Online]. Available: https://www.lumerical.com/products/